# Diseño e implementación de una arquitectura RISC-V en FPGA

#### **PROBLEMA**

Todo sistema embebido que se usa hoy en día tiene como corazón un procesador ya sea parte de un SOC,FPGA o un DSP. Ese procesador tiene como fundamento un set de instrucciones arraigado a las políticas de la compañía que lo administra ya sea ARM, Intel o AMD. Esto deja a los diseñadores externos poco espacio para hacer modificaciones y eleva el costo.

#### **OBJETIVO GENERAL**

Crear un bloque de propiedad intelectual en HDL libre que pueda se usado como base para crear un procesador mas potente o directamente ya sea en un chip o una FPGA.

#### Formato instrucciones RISCV

| 31         | 30           | 25 24 | 21      | 20  | 19         | 15 14      | 1      | 12 11    | 8      | 7       | 6      | 0  |

|------------|--------------|-------|---------|-----|------------|------------|--------|----------|--------|---------|--------|----|

| funct7     |              |       | rs2     |     | rsl        |            | funct3 |          | rd     |         | opcode |    |

| imm[11:0]  |              |       |         | rsl | rs1 funct3 |            |        | rd       |        |         | de     |    |

| imi        |              | rs2   |         | rsl |            | funct3     |        | imm[4:0] |        | opco    | de     |    |

| imm[12]    | imm[10:      | 5]    | rs2     |     | rsl        |            | funct3 | imn      | n[4:1] | imm[11] | opco   | de |

| imm[31:12] |              |       |         |     |            |            |        |          | rd     |         |        | de |

| imm[20]    | 0] imm[10:1] |       | imm[11] |     | ir         | imm[19:12] |        | rd       |        | opco    | de     |    |

#### **PROPUESTA**

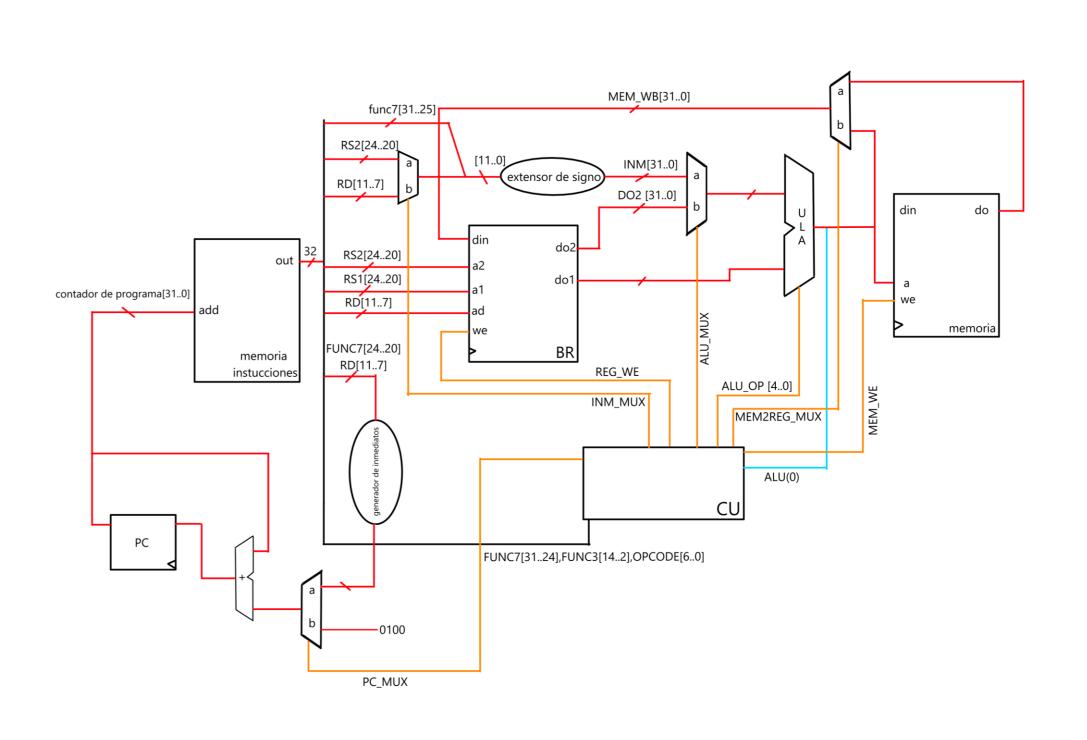

Usando la ISA RISCV que es libre para usarse comercialmente y modificarse al gusto, se diseñara una micro-arquitectura para un procesador monociclo con un pipeline de una sola etapa que sea capaz de ejecutar las instrucciones del RISCV. Luego de eso se realizaran pruebas con diferentes microprocesadores comerciales con el fin de comparar su rendimiento.

### Arquitectura de Programación

## RESULTADOS

### Rendimiento

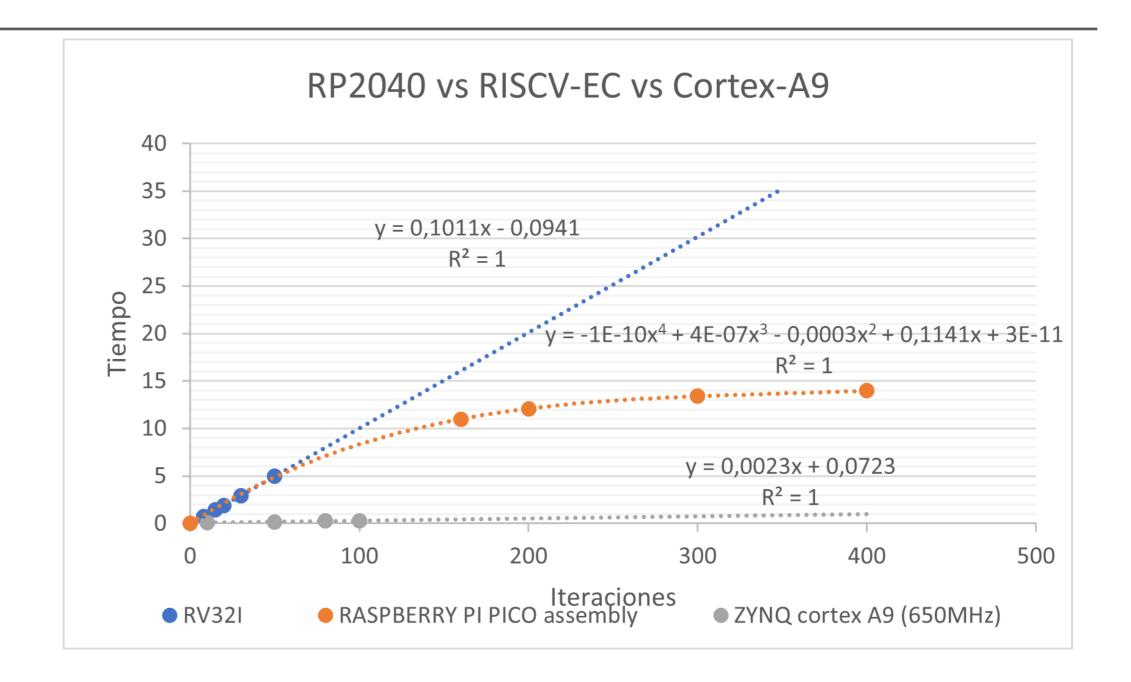

Las pruebas de rendimiento se hicieron usando microcontroladores de gamas y compañías diferentes: Atmega 328p RP2040(ARM-Cortex M0+), Zynq-7000 (ARM-Cortex A9).

### Resultados de Utilización

|                          |       |                         | <b>–</b> a          |                     | • •   |                  |       |                       |  |

|--------------------------|-------|-------------------------|---------------------|---------------------|-------|------------------|-------|-----------------------|--|

| Slice LUTs<br>(53200)    |       |                         | F7 Muxes<br>(26600) | F8 Muxes<br>(13300) |       | Slice<br>(13300) |       | LUT as Log<br>(53200) |  |

| 3.69%                    | 2.36% |                         | 0.77%               | 0.24%               |       | 7.03%            |       | 3.20%                 |  |

| 0.84%                    | 0.70% |                         | 0.00%               | 0.00%               |       | 1.76%            |       | 0.80%                 |  |

| 2.84%                    | 1.66% |                         | 0.77%               | (                   | 0.24% |                  | %     | 2.40%                 |  |

| LUT as Memory<br>(17400) |       | Block RAN<br>Tile (140) | 7.57                | Bonded IOB<br>(125) |       | CTRL B:          |       | CANE2<br>(4)          |  |

| 1.48%                    |       | 1.079                   | % (                 | 0.80%               |       | 9.38%            |       | 25.00%                |  |

| 0.14%                    |       | 0.009                   | % (                 | 0.00%               |       | 3.13%            | 25.00 |                       |  |

| 1.34%                    |       | 1.079                   | % (                 | 0.00%               |       | 3.13%            |       | 0.00%                 |  |

• El costo de recursos en la FPGA es bajo. Por lo que se pueden tener mas de una instancia corriendo en paralelo.

## CONCLUSIONES

- En una FPGA mas pequeña se pueden introducir varias instancias del procesador. Dando como resultado un procesador con un nivel de paralelismo mayor a los microcontroladores que se usaron en la comparativa.

- El procesador con la arquitectura propuesta es mas lento debido a la limitante física de la frecuencia de reloj que presenta la FPGA en comparación con los otras implementaciones en chips que usan una frecuencia mas alta.

- Se comprobó que el procesador funciona y corre código ASSEMBLY DE RISC-V .

- Para mejorar la frecuencia de reloj que acepta el procesador se debe implementar un pipeline mas largo.

- Este procesador tiene aplicaciones comerciales ya que puede ser implementado en varias instancias usando una FPGA